I2C Overview

PHPoC provides I2C, two lines bus interface.

I2C Data Structure

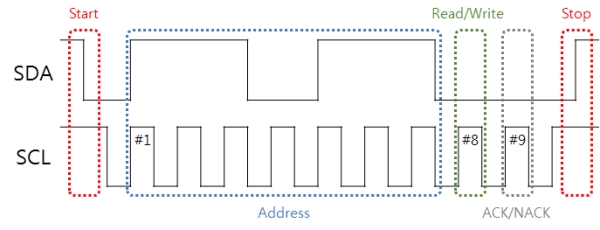

I2C data is always sent in 8-bit unit. Structure of I2C data is as follows:

Start and Stop Conditions

Start and stop conditions of I2C are as follows:

| Condition | SCL | SDA |

|---|---|---|

| Start | HIGH | HIGH > LOW |

| Stop | HIGH | LOW > HIGH |

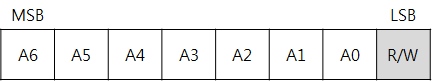

Slave Addressing

PHPoC uses 7-bit slave addressing. The LSB of address byte defines that the frame is for reading or for writing.

Read / Write Conditions

I2C communication consist of reading or writing data from a master.

| Division | SCL | SDA |

|---|---|---|

| Read | 8th bit - HIGH | HIGH |

| Write | 8th bit - HIGH | LOW |

ACK / NACK

Both an I2C master and a slave send acknowledgement (ACK) when receive 8 bits data. Correct acknowledgement is implemented by output HIGH on 9th bit. If the state of bus is HIGH, has not received data yet.

| Division | SCL | SDA |

|---|---|---|

| Acknowledgement(ACK) | 9th bit - HIGH | LOW |

| No Acknowledgement (NACK) | 9th bit - HIGH | HIGH |

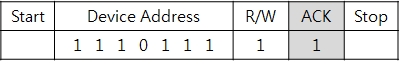

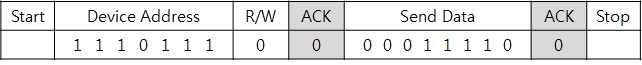

I2C Commuication Scenario

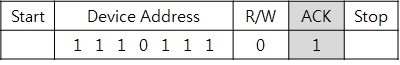

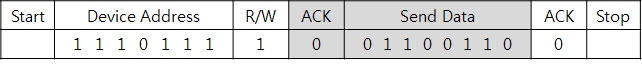

4 different scenarios of I2C communication are as follows. In the scenarios below, white background areas are a master's output and gray background areas are a slave's output.

Success to Write Data

Fail to Write Data

Success to Read Data

Fail to Read Data